Impact of User-mode Memory Registration (UMR) based tuning

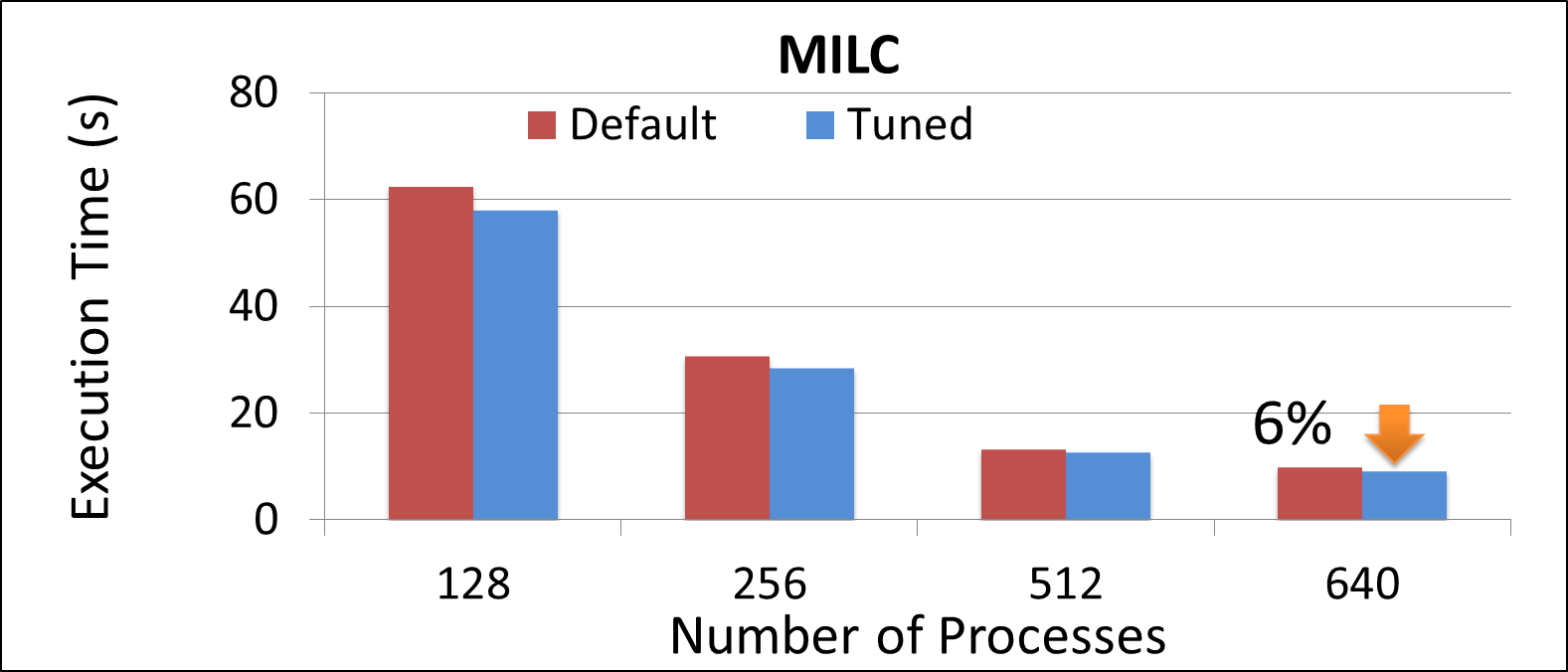

Impact of User-mode Memory Registration (UMR) based tuning on performance of MILC

- Non-contiguous data processing is very common in HPC applications. MVAPICH2 offers efficient designs for MPI Dataype support using novel hardware features such as UMR

- UMR-based protocol selection benefits the MILC application. We see 4% and 6% improvement in execution time at 512 and 640 processors, respectively

Library Version: MVAPICH2-X 2.2b

Runtime Flags: MV2_USE_UMR=1

System Details: The experimental cluster consists of 32 Ivy Bridge Compute nodes interconnected by Mellanox FDR. The Intel Ivy Bridge processors consist of Xeon dual ten-core sockets operating at 2.80GHz with 32GB RAM and Mellanox OFED version 3.2-1.0.1.1.

Tags: MILC

Submitted by Mingzhe Li @ OSU

Last Modified April 19, 2016, 10:03 a.m.