# SCALABLE AND HIGH-PERFORMANCE MPI DESIGN FOR VERY LARGE INFINIBAND CLUSTERS

## DISSERTATION

Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the Graduate School of The Ohio State University

By

Sayantan Sur, B. Tech

\* \* \* \* \*

The Ohio State University

2007

Dissertation Committee: Approved by

Prof. D. K. Panda, Adviser

Prof. P. Sadayappan

Prof. S. Parthasarathy

Adviser Graduate Program in Computer Science and

Engineering

© Copyright by Sayantan Sur 2007

#### ABSTRACT

In the past decade, rapid advances have taken place in the field of computer and network design enabling us to connect thousands of computers together to form high-performance clusters. These clusters are used to solve computationally challenging scientific problems. The Message Passing Interface (MPI) is a popular model to write applications for these clusters. There are a vast array of scientific applications which use MPI on clusters. As the applications operate on larger and more complex data, the size of the compute clusters is scaling higher and higher. Thus, in order to enable the best performance to these scientific applications, it is very critical for the design of the MPI libraries be extremely scalable and high-performance.

InfiniBand is a cluster interconnect which is based on open-standards and gaining rapid acceptance. This dissertation presents novel designs based on the new features offered by InfiniBand, in order to design scalable and high-performance MPI libraries for large-scale clusters with tens-of-thousands of nodes. Methods developed in this dissertation have been applied towards reduction in overall resource consumption, increased overlap of computation and communication, improved performance of collective operations and finally designing application-level benchmarks to make efficient use of modern networking technology. Software developed as a part of this dissertation is available in MVAPICH, which is a popular open-source implementation of MPI over InfiniBand and is used by several hundred top computing sites all around the world.

Dedicated to all my family and friends

### ACKNOWLEDGMENTS

I would like to thank my adviser, Prof. D. K. Panda for guiding me throughout the duration of my PhD study. I'm thankful for all the efforts he took for my dissertation. I would like to thank him for his friendship and counsel during the past years.

I would like to thank my committee members Prof. P. Sadayappan and Dr. S. Parthasarathy for their valuable guidance and suggestions.

I'm grateful for financial support by National Science Foundation (NSF) and Department of Energy (DOE).

I'm thankful to Dr. Bill Gropp, Dr. Rajeev Thakur and Dr. Bill Magro for their support and guidance during my summer internships.

I'm especially thankful to Dr. Hyun-Wook Jin, who was not only a great mentor, but a close friend. I'm grateful to have had Dr. Darius Buntinas as a mentor during my first year of graduate study.

I would like to thank all my senior Nowlab members for their patience and guidance, Dr. Pavan Balaji, Dr. Jiuxing Liu, Dr. Jiesheng Wu, Dr. Weikuan Yu, Sushmita Kini and Bala. I would also like to thank all my colleagues Karthik Vaidyanathan, Abhinav Vishnu, Amith Mamidala, Sundeep Narravula, Gopal Santhanaraman, Savitha Krishnamoorthy, Weihang Jiang, Wei Huang, Qi Gao, Matt Koop, Lei Chai and Ranjit Noronha. I'm especially grateful to Matt and Lei and I'm lucky to have collaborated closely with them.

During all these years, I met many people at Ohio State, some of whom are very close friends, and I'm thankful for all their love and support: Nawab, Bidisha, Borun, Ashwini and Naveen.

Finally, I would like to thank my family members, Swati (my mom), Santanu (my dad) and Sohini (my sister). I would not have had made it this far without their love and support.

## **VITA**

| September 29, 1979Born - Calcutta, India. |                                                                                              |  |  |  |  |

|-------------------------------------------|----------------------------------------------------------------------------------------------|--|--|--|--|

| August 1997 - July 2001                   | B.Tech Electrical and Electronics Engineering, Regional Engineering College, Calicut, India. |  |  |  |  |

| August 2001 - July 2002                   | . Member of Technical Staff, Sun Microsystems, India.                                        |  |  |  |  |

| August 2002 - June 2003                   | 02 - June 2003 Graduate Teaching Associate, The Ohio State University.                       |  |  |  |  |

| June 2005 - September 2005                | . Summer Intern,<br>Intel Corp, Urbana-Champaign, IL.                                        |  |  |  |  |

| June 2006 - September 2006                | . Summer Intern, Argonne National Laboratory, Chicago, IL.                                   |  |  |  |  |

| June 2003 - August 2007                   | . Graduate Research Associate,<br>The Ohio State University.                                 |  |  |  |  |

## **PUBLICATIONS**

W. Yu, S. Sur, D. K. Panda, R. T. Aulwes and R. L. Graham, "High Performance Broadcast Support in LA-MPI over Quadrics". *International Journal of High Performance Computer Applications*, Winter 2005.

M. Koop, S. Sur and D. K. Panda, "Zero-Copy Protocol for MPI using InfiniBand Unreliable Datagram", IEEE International Conference on Cluster Computing (Cluster 2007), Austin TX.

S. Sur, M. Koop, L. Chai and D. K. Panda, "Performance Analysis and Evaluation of Mellanox ConnectX InfiniBand Architecture with Multi-Core Platforms", 15th Symposium on High-Performance Interconnects (HOTI-15), August 2007.

- M. Koop, S. Sur, Q. Gao and D. K. Panda, "High Performance MPI Design using Unreliable Datagram for Ultra-Scale InfiniBand Clusters", 21st Int'l ACM Conference on Supercomputing, June 2007.

- S. Sur, M. Koop and D. K. Panda, "High-Performance and Scalable MPI over InfiniBand with Reduced Memory Usage: An In-Depth Performance Analysis", SuperComputing (SC), November 11-17, 2006, Tampa, Florida, USA.

- S. Sur, L. Chai, H.-W. Jin and D. K. Panda, "Shared Receive Queue Based Scalable MPI Design for InfiniBand Clusters", International Parallel and Distributed Processing Symposium (IPDPS 2006), April 25-29, 2006, Rhodes Island, Greece.

- S. Sur, H.-W. Jin, L. Chai and D. K. Panda, "RDMA Read Based Rendezvous Protocol for MPI over InfiniBand: Design Alternatives and Benefits", Symposium on Principles and Practice of Parallel Programming (PPOPP 2006), March 29-31, 2006, Manhattan, New York City.

- S. Sur, U. Bondhugula, A. Mamidala, H.-W. Jin, and D. K. Panda, "High Performance RDMA Based All-to-all Broadcast for InfiniBand Clusters", International Conference on High Performance Computing (HiPC 2005), December 18-21, 2005, Goa, India.

- S. Sur, A. Vishnu, H.-W. Jin, W. Huang and D. K. Panda, "Can Memory-Less Network Adapters Benefit Next-Generation InfiniBand Systems?", Hot Interconnects Symposium, August 17-19, 2005, Stanford University, Palo Alto, California.

- H.-W. Jin, S. Sur, L. Chai and D. K. Panda, "LiMIC: Support for High-Performance MPI Intra-Node Communication on Linux Clusters", International Conference on Parallel Processing (ICPP-05), June 14-17, 2005, Oslo, Norway.

- L. Chai, S. Sur, H.-W. Jin and D. K. Panda, "Analysis of Design Considerations for Optimizing Multi-Channel MPI over InfiniBand", Workshop on Communication Architecture for Clusters (CAC 2005); In Conjunction with IPDPS, April 4-8, 2005, Denver, Colorado.

- S. Sur, H.-W. Jin, and D.K. Panda, "Efficient and Scalable All-to-All Exchange for InfiniBand-based Clusters", International Conference on Parallel Processing (ICPP-04), Aug. 15-18, 2004, Montreal, Quebec, Canada.

- W. Yu, S. Sur, D. K. Panda, R. T. Aulwes and R. L. Graham, "High Performance Broadcast Support in LA-MPI over Quadrics", In Los Alamos Computer Science Institute Symposium, (LACSI'03), Santa Fe, New Mexico, October 2003.

# FIELDS OF STUDY

Major Field: Computer Science and Engineering

## Studies in:

Computer Architecture Prof. D. K. Panda Computer Networks Prof. D. Xuan

Software Systems Prof. P. Sadayappan

# TABLE OF CONTENTS

|        |       | P                                              | age  |

|--------|-------|------------------------------------------------|------|

| Abstr  | act . |                                                | ii   |

| Dedic  | ation | n                                              | iii  |

| Ackno  | owled | dgments                                        | iv   |

| Vita   |       |                                                | vi   |

| List o | f Tal | bles                                           | xiii |

| List o | f Fig | gures                                          | xiv  |

| Chapt  | ters: |                                                |      |

| 1. I   | [ntro | $\operatorname{duction}$                       | 1    |

|        | 1.1   | Overview of MPI                                | 3    |

|        |       | 1.1.1 Point-to-Point Communication             | 4    |

|        |       | 1.1.2 Collective Communication                 | 5    |

|        |       | 1.1.3 MPI Design Issues                        | 5    |

|        | 1.2   | Overview of InfiniBand                         | 7    |

|        |       | 1.2.1 Communication Semantics                  | 9    |

|        |       | 1.2.2 Transport Services                       | 10   |

|        |       | 1.2.3 Shared Receive Queue                     | 11   |

|        |       | 1.2.4 Memory Registration                      | 12   |

|        |       | 1.2.5 Completion and Event Handling Mechanisms | 12   |

|        | 1.3   | Problem Statement                              | 13   |

|        | 1.4   | Research Approaches                            | 16   |

|        | 1.5   | Dissertation Overview                          | 17   |

| 2. | Impi | roving Computation and Communication Overlap             | 20 |

|----|------|----------------------------------------------------------|----|

|    | 2.1  | Background                                               | 21 |

|    |      |                                                          | 21 |

|    |      | 2.1.2 Overview of InfiniBand RDMA-Write and RDMA-Read    | 22 |

|    | 2.2  | Current Approaches and their Limitations                 | 22 |

|    | 2.3  | e e                                                      | 23 |

|    |      | 2.3.1 RDMA Read with Interrupt Based Rendezvous Protocol | 26 |

|    | 2.4  | Performance Evaluation                                   | 28 |

|    |      | 2.4.1 Computation and Communication Overlap Performance  | 29 |

|    |      | 2.4.2 Application level Evaluation                       | 34 |

|    | 2.5  | Summary                                                  | 35 |

| 3. | Impi | roving Performance of All-to-All Communications          | 37 |

|    | 3.1  | Background                                               | 38 |

|    |      |                                                          | 38 |

|    | 3.2  |                                                          | 40 |

|    | 3.3  |                                                          | 40 |

|    |      |                                                          | 42 |

|    |      | O .                                                      | 43 |

|    |      |                                                          | 46 |

|    | 3.4  |                                                          | 48 |

|    |      |                                                          | 48 |

|    |      |                                                          | 49 |

|    |      | 9                                                        | 50 |

|    | 3.5  |                                                          | 52 |

| 4. | Impi | roving Performance of All-to-All Broadcast               | 53 |

|    | 4.1  | Background                                               | 54 |

|    | 1.1  |                                                          | 54 |

|    | 4.2  |                                                          | 56 |

|    | 1.2  |                                                          | 56 |

|    |      |                                                          | 57 |

|    |      | 1                                                        | 57 |

|    |      | ~                                                        | 58 |

|    | 4.3  | 1 0                                                      | 58 |

|    | 4.U  | 1                                                        | 58 |

|    |      |                                                          | 60 |

|    | 4.4  |                                                          | 60 |

|    | 4.4  | - LVATOUHIGHV5 TVGHUGHOH                                 | w  |

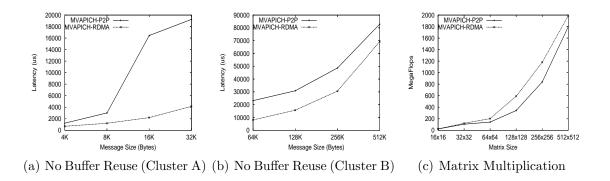

|    |       | 4.4.1   | Latency benchmark for MPI_Allgather                       | . 61  |

|----|-------|---------|-----------------------------------------------------------|-------|

|    |       | 4.4.2   | MPI_Allgather latency with no buffer reuse                | . 62  |

|    |       | 4.4.3   | Matrix Multiplication Application Kernel                  | . 63  |

|    | 4.5   | Summ    | nary                                                      | . 63  |

| 5. | Scala | able Co | ommunication Buffer Management Techniques                 | . 67  |

|    | 5.1   | Overv   | riew of Shared Receive Queues                             | . 69  |

|    | 5.2   |         | nt Approaches and Limitations                             |       |

|    | 5.3   |         | its of using Shared Receive Queues                        |       |

|    | 5.4   |         | Design Alternatives using Shared Receive Queues           |       |

|    |       | 5.4.1   | Proposed SRQ Refilling Mechanism                          |       |

|    |       | 5.4.2   | Proposed Design of SRQ Limit Threshold                    |       |

|    |       | 5.4.3   | Analytical Model for Memory Usage Estimation              |       |

|    | 5.5   | Perfor  | rmance Results                                            |       |

|    |       | 5.5.1   | Experimental Environment                                  |       |

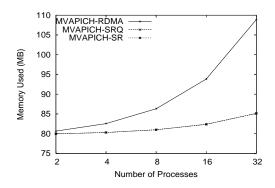

|    |       | 5.5.2   | Startup Memory Utilization                                |       |

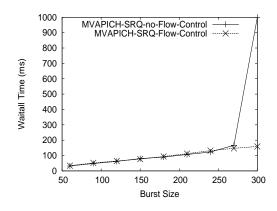

|    |       | 5.5.3   | Flow Control                                              |       |

|    |       | 5.5.4   | NAS Benchmarks                                            |       |

|    |       | 5.5.5   | High Performance Linpack                                  |       |

|    | 5.6   | Summ    | nary                                                      |       |

| 6. | In D  | ooth So | calability Analysis of MPI Design                         | . 88  |

| 0. | шъ    | сриг ос | Salability Tiliarysis of Mil i Design                     | . 00  |

|    | 6.1   | Overv   | riew of MPI Design                                        | . 89  |

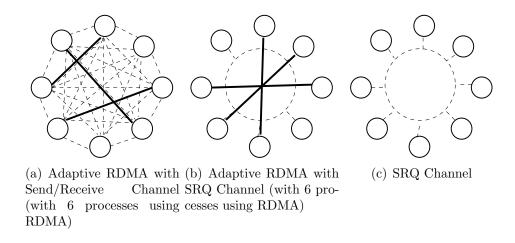

|    |       | 6.1.1   | Adaptive RDMA with Send/Receive Channel                   | . 91  |

|    |       | 6.1.2   | Adaptive RDMA with SRQ Channel                            | . 92  |

|    |       | 6.1.3   | SRQ Channel                                               | . 93  |

|    | 6.2   | Perfor  | rmance Evaluation Parameters                              | . 93  |

|    | 6.3   | Perfor  | rmance Results                                            | . 95  |

|    |       | 6.3.1   | NAS Benchmarks                                            | . 96  |

|    |       | 6.3.2   | NAMD                                                      | . 102 |

|    |       | 6.3.3   | High Performance Linpack (HPL)                            | . 104 |

|    |       | 6.3.4   | Scalability Analysis                                      | . 105 |

|    | 6.4   | Summ    | nary                                                      | . 107 |

| 7. | Opti  | mizing  | MPI applications: A Case Study With Two HPCC Benchmarks . | . 108 |

|    | 7.1   | Overv   | riew of HPCC Benchmarks                                   | . 109 |

|    |       | 7.1.1   | Overview of HPL Benchmark                                 |       |

|    |       | 7.1.2   | Overview of RandomAccess Benchmark                        |       |

|    | 7 2   | -       | viow of MPI Library Optimizations                         | 119   |

|        |       | 7.2.1    | Optimizations for Computation/Communication Overlap | 112 |

|--------|-------|----------|-----------------------------------------------------|-----|

|        |       | 7.2.2    | Optimizations to Communication Buffer Management    | 112 |

|        | 7.3   | Modifi   | ications to HPCC Benchmarks                         | 113 |

|        |       | 7.3.1    | Modifications to HPL                                | 113 |

|        |       | 7.3.2    | Modifications to RandomAccess                       | 114 |

|        | 7.4   | Perfor   | mance Results                                       | 115 |

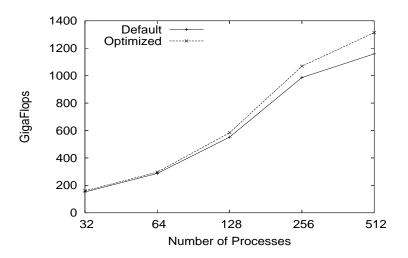

|        |       | 7.4.1    | Performance Results for HPL                         | 115 |

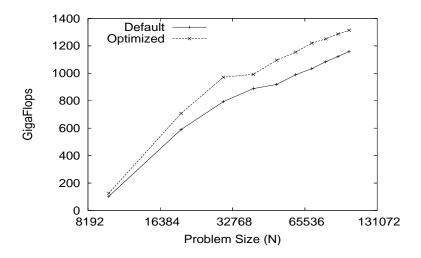

|        |       | 7.4.2    | Performance Results for RandomAccess                | 117 |

|        | 7.5   | Summ     | ary                                                 | 118 |

| 9.     | Conc  | clusions | and Future Research Directions                      | 123 |

|        | 9.1   | Summ     | ary of Research Contributions                       | 123 |

|        |       | 9.1.1    | Improving Computation/Communication Overlap         | 124 |

|        |       | 9.1.2    | Improving Performance of Collective Operations      | 124 |

|        |       | 9.1.3    | Scalable Communication Buffer Management Techniques | 125 |

|        |       | 9.1.4    | In-Depth Scalability Analysis of MPI Design         | 125 |

|        |       | 9.1.5    | Optimizing end MPI Applications/Benchmarks          | 125 |

|        | 9.2   | Future   | e Research Directions                               | 126 |

| Biblic | ogran | hv       |                                                     | 128 |

# LIST OF TABLES

| Tab | le                                                                       | Page |

|-----|--------------------------------------------------------------------------|------|

| 1.1 | Comparison of IBA Transport Types                                        | 11   |

| 6.1 | Profiling Results on 64 processes of NAS (Class B), NAMD (apoa1) and HPI | . 95 |

| 6.2 | Profiling Results for SuperLU                                            | 100  |

# LIST OF FIGURES

| Fig | ure                                                                    | Page |

|-----|------------------------------------------------------------------------|------|

| 1.1 | InfiniBand Architecture (Courtesy IBTA)                                | . 8  |

| 1.2 | IBA Communication Stack (Courtesy IBTA)                                | . 9  |

| 1.3 | Problem Space for this Dissertation                                    | . 13 |

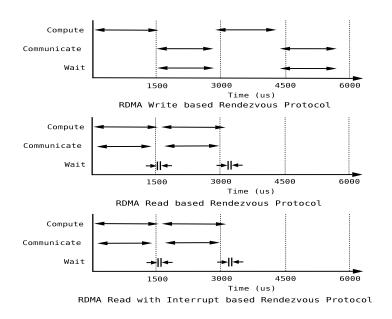

| 2.1 | MVAPICH Rendezvous Protocol and its Limitations                        | . 24 |

| 2.2 | RDMA Read Based Rendezvous Protocol                                    | . 26 |

| 2.3 | RDMA Read with Interrupt based Rendezvous Protocol                     | . 29 |

| 2.4 | Sender Communication and Computation Overlap Performance               | . 31 |

| 2.5 | Receiver Communication and Computation Overlap Performance             | . 31 |

| 2.6 | Computation and Communication Overlap (Sender) with Time Stamps $$     | . 32 |

| 2.7 | Computation and Communication Overlap (Receiver) with Time Stamps $$ . | . 32 |

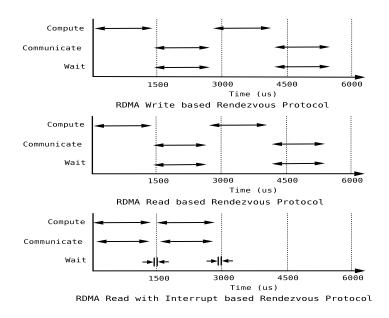

| 2.8 | Application Level Evaluation for Rendezvous Protocol Designs           | . 35 |

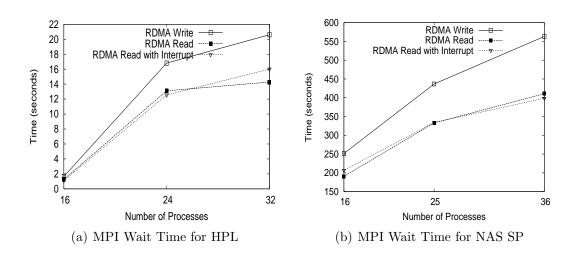

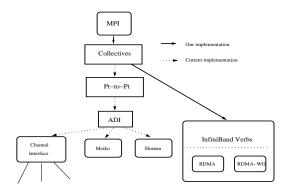

| 3.1 | Layered Design of Collective Operations and Associated Overheads       | . 41 |

| 3.2 | Proposed implementation path for Collectives                           | . 41 |

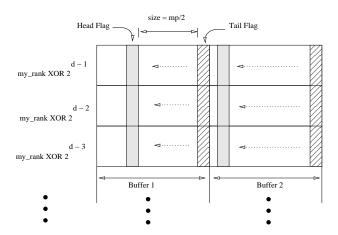

| 3.3 | Buffer arrangement for Hypercube Algorithm                             | . 44 |

| 3.4 | Managing Buffer pointers                                               | . 45 |

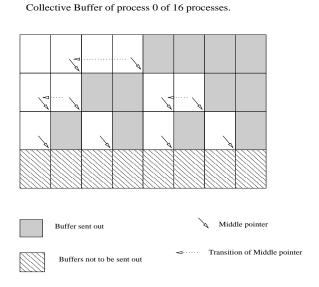

| 3.5 | Direct Eager Mechanism                                                                  | 47 |

|-----|-----------------------------------------------------------------------------------------|----|

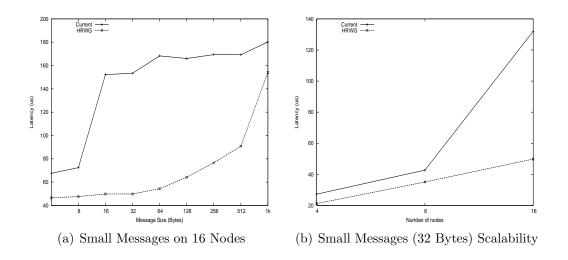

| 3.6 | Small Message Performance Benefits for All-to-all Personalized Communication            | 49 |

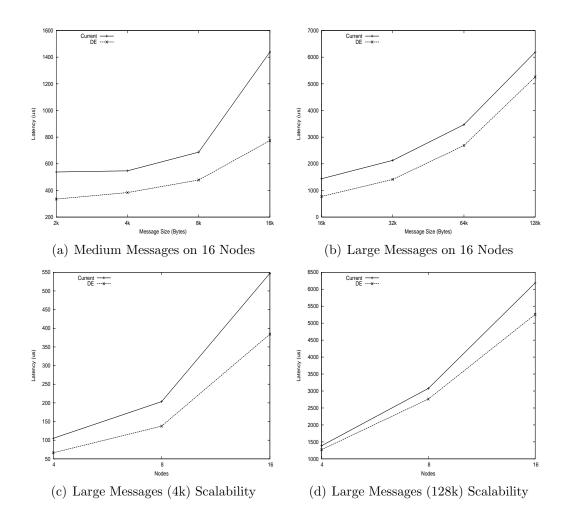

| 3.7 | Medium and Large Message Performance Benefits for All-to-all Personalized Communication | 51 |

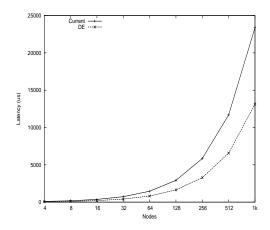

| 3.8 | Performance for 4k message among 1k processes                                           | 51 |

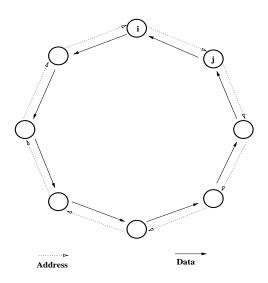

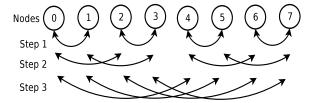

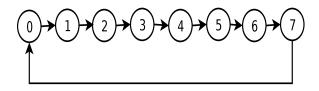

| 4.1 | Recursive Doubling Algorithm for MPI_Allgather                                          | 55 |

| 4.2 | Ring Algorithm for MPI_Allgather                                                        | 56 |

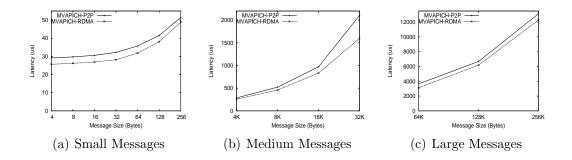

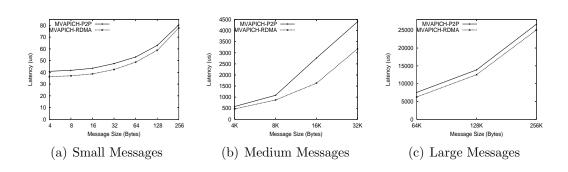

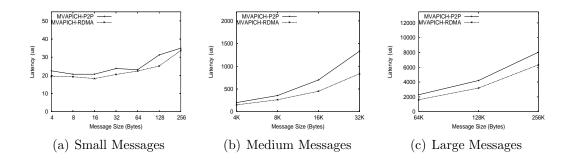

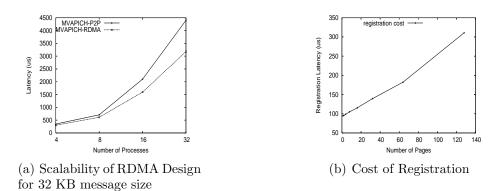

| 4.3 | MPI_Allgather Performance on 16 Processes (Cluster A)                                   | 64 |

| 4.4 | MPI_Allgather Performance on 32 Processes (Cluster A)                                   | 64 |

| 4.5 | MPI_Allgather Performance on 16 Processes (Cluster B)                                   | 64 |

| 4.6 | Scalability and Registration Cost on Cluster A                                          | 65 |

| 4.7 | Impact of Buffer Registration and Performance of Matrix Multiplication                  | 65 |

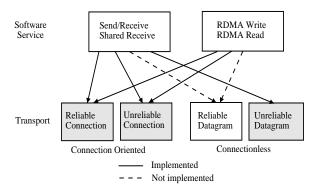

| 5.1 | IBA Transport and Software Services                                                     | 69 |

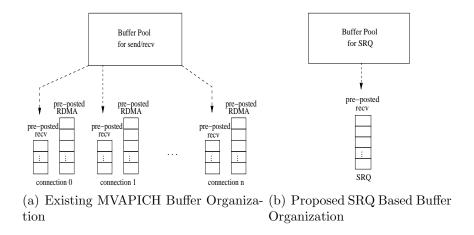

| 5.2 | Comparison of Buffer Management Models                                                  | 72 |

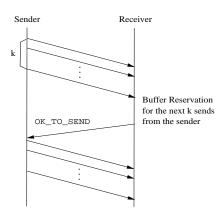

| 5.3 | Explicit ACK mechanism                                                                  | 74 |

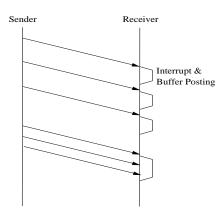

| 5.4 | Interrupt Based Progress                                                                | 75 |

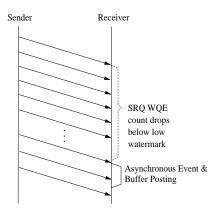

| 5.5 | SRQ Limit Event Based Design                                                            | 76 |

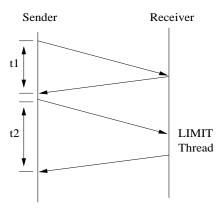

| 5.6 | LIMIT Thread Wakeup Latency                                                             | 77 |

| 5.7 | Memory Utilization Experiment                                                           | 81 |

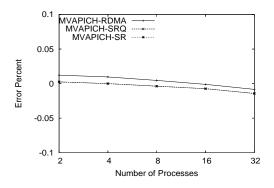

| 5.8 | Error Margin of Analytical Model                                                        | 82 |

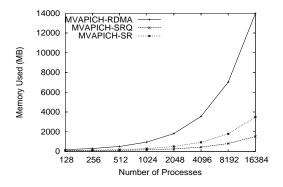

| 5.9 | Estimation of memory consumption on very large clusters                                 | 82 |

| 5.10 | MPI_Waitall Time comparison                                         | 84  |

|------|---------------------------------------------------------------------|-----|

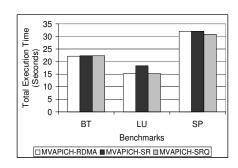

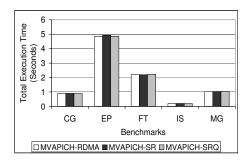

| 5.11 | NAS Benchmarks Class A Total Execution Time (BT, LU, SP)            | 85  |

| 5.12 | NAS Benchmarks Class A Total Execution Time (CG, EP, FT, IS, MG) $$ | 85  |

| 5.13 | High Performance Linpack                                            | 87  |

| 6.1  | Various Eager Protocol Designs in MVAPICH                           | 91  |

| 6.2  | Performance of NAS Benchmarks                                       | 97  |

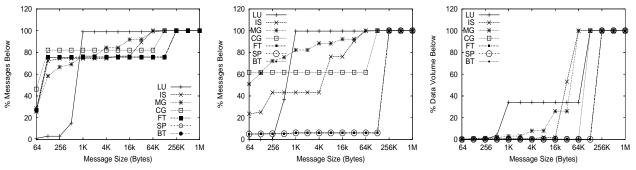

| 6.3  | Network-Level Message and Volume Profile of NAS Benchmarks          | 98  |

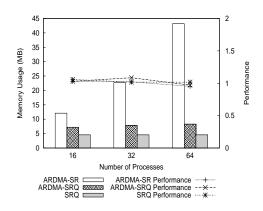

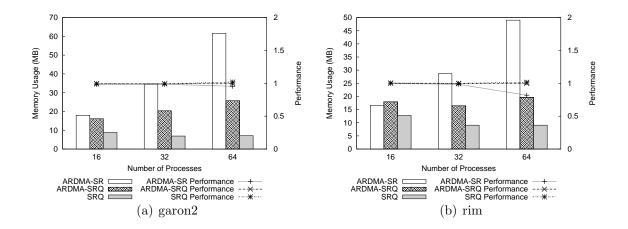

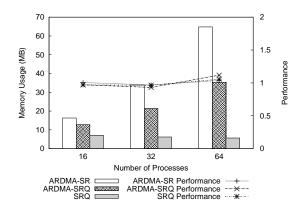

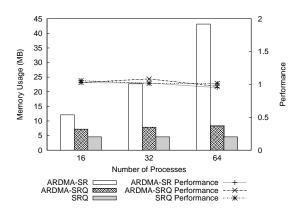

| 6.4  | Memory Usage and Performance of SuperLU                             | 101 |

| 6.5  | Network-Level Message and Volume Profile of SuperLU Datasets        | 101 |

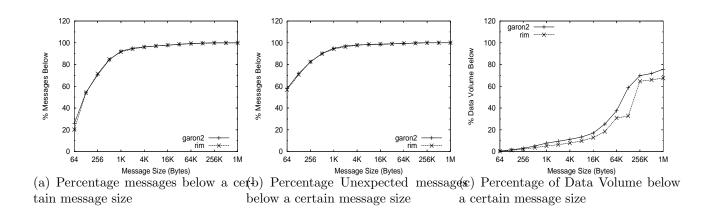

| 6.6  | Network-Level Message and Volume Profile of NAMD Datasets           | 102 |

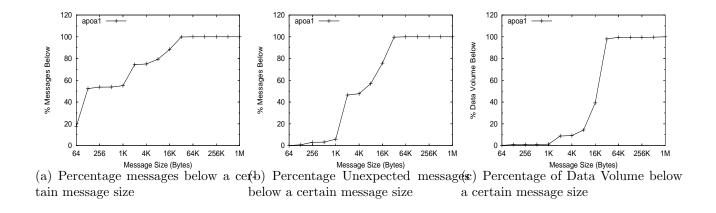

| 6.7  | Performance of NAMD (apoa1)                                         | 103 |

| 6.8  | Performance of HPL                                                  | 104 |

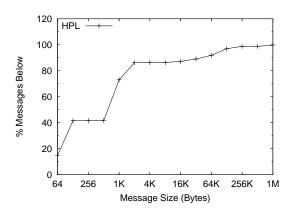

| 6.9  | Message Size Distribution for HPL                                   | 105 |

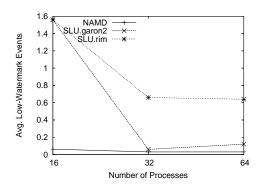

| 6.10 | Avg. Low-Watermark Events                                           | 106 |

| 7.1  | HPL Broadcast Algorithm                                             | 110 |

| 7.2  | HPL Results with increasing number of processes                     | 116 |

| 7.3  | HPL Results on 512 processes with increasing problem size           | 117 |

| 7.4  | Performance of RandomAccess Benchmark                               | 119 |

## CHAPTER 1

#### INTRODUCTION

Modern day existence is enabled by applications such as weather forecasting, Internet search, e-commerce, drug research, space exploration, data-mining, fluid dynamics simulations, etc. It is almost impossible for us to imagine our daily life without these applications. All these applications depend upon High-Performance Computing (HPC) systems. These systems employ up to several thousand computers connected together by modern networking technologies such as Gigabit Ethernet, Myrinet [7], InfiniBand [17] etc., to execute these applications. Modern HPC systems operate at "Terascale" (10<sup>12</sup> calculations per second). Although computation power available today seems to be plentiful, it is not enough to satiate the need of demanding applications such as weather forecasting. Due to inadequate computation power, weather cannot be accurately predicted beyond a few days, resulting in delayed advisories or bad predictions. One can expect that tomorrow's applications will be even more challenging, requiring HPC systems to reach "PetaScale" (10<sup>15</sup> calculations per second).

One of the popular types of parallel computers is called a "Cluster". Clusters are built out of commodity components taken off-the-shelf. The high volume of commodity components brings down the cost of clusters significantly and boosts the cost-to-performance ratio. In fact, currently 373 of the top 500 most powerful computers in the world [45] are clusters. The

adoption of clusters for very high-end computing has also been encouraged by availability of high-performance interconnects which provide communication support for these clusters. Recent advances in interconnection technology can boost the size of clusters to tens-of-thousands of nodes. In order to scale up HPC systems to PetaScale, one of the major challenges is to provide scalable software environments under which parallel applications can execute. The Message Passing Interface (MPI) [30] is one of the most popular software environment for HPC systems, and is used by almost all HPC applications. Thus, it is crucial that the design and implementation of MPI is scalable, so that the applications utilizing MPI can also scale accordingly.

InfiniBand [17] is a cluster interconnect which is based on open standards and is gaining widespread acceptance. It offers several new features which make it desirable for High Performance Computing. MVAPICH [34] is a popular implementation of MPI over InfiniBand which is used by several hundred of the top computing sites all around the world. The basic design of MVAPICH was proposed by J. Liu et al [24]. Since the initial design, the scale of the InfiniBand clusters in production use has grown from a few hundreds-of-nodes to several thousands of nodes. In fact, InfiniBand clusters with tens-of-thousands of nodes are being built for use by the end of this year. As the order-of-magnitude of the clusters has increased, the design of the MPI layer needs to ever more scalable and high-performance. In this dissertation, we present our studies on how to design a high-performance and scalable MPI communication layer while leveraging novel features offered by InfiniBand.

The rest of this Chapter is organized as follows. First we provide an overview of MPI and relevant scalability issues. We then provide an overview of InfiniBand and its modern networking mechanisms. Following that, we present the problem statement and the research approaches. Finally, we provide an overview of this dissertation.

## 1.1 Overview of MPI

The message passing model of parallel computing requires explicit communication between processes involved in the computation. This model has been thought to be one of the most effective methods to scale a parallel computer up. Message passing was used in early supercomputers in the 1980s. However, during that period, nearly every supercomputer had a different way of doing message passing, and applications were not portable from one parallel computer to the other. To rectify this situation and to pave the way for developing high-performance scientific applications, efforts were started in the early 1990s to standardize the interface which is used by applications to send and receive messages. The result of the standardization process is the Message Passing Interface (MPI) [30]. An extension to the initial specification is also available as MPI2 [31]. MPI provides an application programming interface (API) for the Fortran, C and C++ languages.

MPI has since established itself as the de-facto standard of parallel computing. Nearly all scientific computation applications are written using MPI, and many higher-level communication libraries require MPI. MPI is very portable and has been ported to nearly all parallel computer architectures. There is a wide variety of quality MPI implementations available as open-source: MPICH [15], MPICH2 [27], MVAPICH, MVAPICH2 [34], OpenMPI [13]. MPI provides two major modes of communication, point-to-point and collective. In point-to-point communication, individual pairs of processes are involved in sending and receiving messages. In collective communication operations, groups of processes are involved in the data exchange. In this section, we describe the major communication modes offered by MPI in detail, their semantics and issues in designing scalable and high-performance MPI.

## 1.1.1 Point-to-Point Communication

In an MPI program, two processes can exchange messages using point-to-point communication primitives. The process wishing to send a message, can send it using a function MPI\_Send. The receiving process may retrieve this message with a matching MPI\_Recv. Messages are matched by a three-tuple source, tag and context. The "source" indicates the process where the message originated. The "tag" is a user supplied integer value and can be used to separate different messages. The "context" is the group of the processes the sending process belongs to.

MPI\_Send and MPI\_Recv are the most commonly used MPI functions. However, there are variations of these calls. MPI\_Send and MPI\_Recv are often called as the "blocking" mode calls, i.e. the sending and receiving processes block on these calls until the corresponding operations complete, or the message buffers can be reclaimed by the application. MPI\_Isend and MPI\_Irecv are the asynchronous versions of the send and receive calls. Using these, the application can initiate send and receive operations while continuing to perform its own computation. The MPI library will attempt to make progress in the meanwhile and can complete these operations. In order to finish the asynchronous operations, the application then needs to call MPI\_Wait.

The other modes of point-to-point calls are *synchronous*, *buffered* and *ready*. In the synchronous mode, the application is guaranteed that the network/message transfer operations relating to the send/receive are complete before control returns to the application. This mode is activated using MPI\_Ssend and is primarily used for debugging MPI applications which erroneously have assumed internal MPI buffering. The buffered mode allows applications to provide explicit memory buffers for communication, so that it doesn't have to worry about where the messages may actually be buffered. This is mainly a convenience

function and is activated using MPI\_Bsend. Finally, in the ready mode may be used when the sending process is sure that a matching receive has been posted. This is an attempt to optimize network protocols associated with that send/receive operation. However, in most MPI implementation, the ready send is just mapped to MPI\_Send for the sake of convenience.

#### 1.1.2 Collective Communication

In addition to the point-to-point communication primitives, MPI offers collective communication operations. These functions allow a group of processes to perform communication in a coordinated fashion. Based on the physical network and system topology, these operations can be then highly optimized by the MPI library. The application using these MPI functions then need not be aware of specific platform specific parameters in order to optimize these communication patterns. Examples of collective communication are: MPI\_Alltoall, MPI\_Allgather, MPI\_Bcast, MPI\_Reduce, MPI\_Barrier etc. Thus, the collective operations not only provide a simple and intuitive interface to application programmers but also give MPI implementors a greater opportunity to optimize them.

## 1.1.3 MPI Design Issues

In order to design a high-performance and scalable MPI library, there are many different design issues to consider. In this section, we provide and overview of the general issues that need to be dealt with. In the subsequent sections, we will describe them in depth in context with the InfiniBand Architecture.

#### Communication Buffer Management

MPI assumes a fully connected model. Under this assumption, applications utilizing MPI can send/receive messages from each other at any given moment during the execution.

In order to transmit messages, the MPI library has to ensure that there is some memory space at the receiver where incoming messages land. On the receiving side, the MPI library can then inspect the incoming messages to perform the correct action. The memory space which must be dedicated to receive messages is often referred to as "communication buffers". As the number of processes in the MPI application increases, the amount of buffer space required by the MPI library should not increase dramatically. On the contrary, some limits must be enforced on how much memory is consumed by communication buffers based on how much memory is available at each sending process. Even for process counts in several tens-of-thousands, memory required must be within reasonable limits.

#### Flow Control

As mentioned in the previous section, MPI assumes a fully connected model with processes sending and receiving messages at will. The MPI library should ensure that incoming messages do not totally overwhelm the receiving process. In order to achieve this, the MPI library should impose directly or indirectly some flow control which limits the rate at which communication buffers are consumed from within the MPI library. As the system size scales, overhead imposed by flow control should be as low as possible. In addition, good flow control mechanisms should allow for as much communication to take place as possible before imposing strict limitations on the rate of incoming messages.

#### Communication Protocol Design and Progress

Applications using MPI may send or receive arbitrary sized messages. Internally, MPI uses two major types of protocols. They are called *Eager* and *Rendezvous* protocols. In the eager mode, usually used for small messages, the sending process simply sends the message over to the remote side, where it is temporarily buffered in the communication buffers. The

Rendezvous mode, usually used for larger messages involves a handshake operation before the actual message is sent. This is done in order to guarantee availability of memory at the receiver for the entire message. The internal design of these protocols is key to achieving high-performance and overlap of computation and communication. The overlap indicates that the MPI application is able to continue computing while the MPI library along with the network-interface take on the responsibility of transferring the message, i.e. continue to make progress.

#### **Collective Communication**

Most collective operations are blocking operations, i.e. requiring reception of messages from remote processes. This makes collective operations especially latency sensitive. Accordingly, applications expect that each collective operation be carefully tuned according to the specific platform. While designing collective operations for large system sizes, scalable algorithms and techniques should be employed. There should be as less memory dedicated as possible and it should be reused as much as possible. Finally, for achieving lowest latency, the collective operations can be based on direct network primitives and not on MPI point-to-point operations.

#### 1.2 Overview of InfiniBand

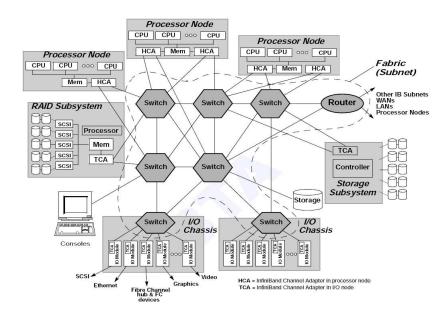

The InfiniBand Architecture [17] (IBA) defines a switched network fabric for interconnecting compute and I/O nodes. In an InfiniBand network, compute and I/O nodes are connected to the fabric using Channel Adapters (CAs). There are two types of CAs: Host Channel Adapters (HCAs) which connect to the compute nodes and Target Channel Adapters (TCAs) which connect to the I/O nodes. IBA describes the service interface between a host channel

adapter and the operating system by a set of semantics called *Verbs*. Verbs describe operations that take place between a CA and its operating system for submitting work requests to the channel adapter and returning completion status. Figure 1.1 depicts the architecture of an InfiniBand network.

Figure 1.1: InfiniBand Architecture (Courtesy IBTA)

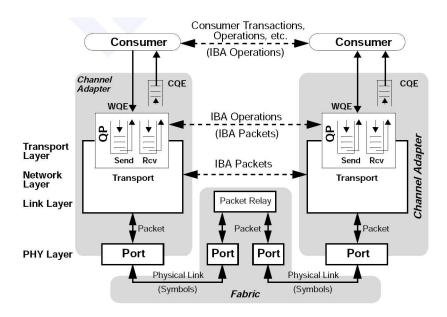

InfiniBand uses a queue based model. A consumer can queue up a set of instructions that the hardware executes. This facility is referred to as a Work Queue (WQ). Work queues are always created in pairs, called a Queue Pair (QP), one for send operations and one for receive operations. In general, the send work queue holds instructions that cause data to be transferred between the consumer's memory and another consumer's memory, and the receive work queue holds instructions about where to place data that is received from another consumer. The completion of WQRs is reported through Completion Queues (CQ).

Figure 1.2 shows a Queue Pair connecting two consumers and communication through the send and the receive queues.

Figure 1.2: IBA Communication Stack (Courtesy IBTA)

#### 1.2.1 Communication Semantics

InfiniBand supports two types of communication semantics. They are called *Channel* and *Memory* semantics. In channel semantics, the sender and the receiver both explicitly place work requests to their QP. After the sender places the send work request, the hardware transfers the data in the corresponding memory area to the receiver end. It is to be noted that the receive work request needs to be present before the sender initiates the data transfer. This restriction is prevalent in most high-performance networks like Myrinet [32], Quadrics [36] etc.

In memory semantics, Remote Direct Memory Access (RDMA) operations are used instead of send/receive operations. These RDMA operations are one-sided and do not require any software involvement at the other side. ie. the other side CPU does not have to issue any work request for the data transfer. Both RDMA Write (write to remote memory location) and RDMA Read (read from remote memory location) are supported in InfiniBand.

## 1.2.2 Transport Services

The InfiniBand architecture supports multiple classes of transport services. A queue pair can be configured with either of these types of transports:

- 1. Reliable Connection (RC)

- 2. Reliable Datagram (RD)

- 3. Unreliable Connection (UC)

- 4. Unreliable Datagram (UD)

- 5. Raw Datagram

Transport services RC and UC are connection oriented. They require a QP to be exclusive to a pair of processes. On the other hand RD and UD are connection-less, i.e. a QP may be used to communicate with as many pairs of processes as possible. Each QP requires a particular set of resources. These resources are mainly to store context information and in case of reliable transports to guarantee reliable, in-order delivery. In general, connection-less transports require lesser resources than connection-oriented transports. The Raw Datagram is used to provide compatibility with other types of networks. For example, IPv6 packets may be tunneled over InfiniBand using this type of transport. The Raw Datagram is out of scope for this proposal.

Table 1.1 compares the various transports provided by IBA. We note that for m processes on n nodes and all processes connected, the RC and UC transports require the most number

| Attribute                   | RC       | RD       | UC         | UD         | Raw Datagram |

|-----------------------------|----------|----------|------------|------------|--------------|

| Scalability (Number of QPs) | $m^2n$   | m        | $m^2n$     | m          | 1            |

| Corrupt Data Detected       | Yes      | Yes      | Yes        | Yes        | Yes          |

| Delivery Guarantee          | Yes      | Yes      | No         | No         | No           |

| Data Loss Detection         | Yes      | Yes      | No         | Yes        | No           |

| Error Recovery              | Reliable | Reliable | Unreliable | Unreliable | Unreliable   |

Table 1.1: Comparison of IBA Transport Types

of QPs. On the other hand RD and UD require much lesser QPs. However, to the best of our knowledge, no InfiniBand hardware currently implements RD. The RC transport provides reliable in order delivery and detection and is suitable for programming models such as MPI which require all processes to be logically connected and provide reliable data transfer.

## 1.2.3 Shared Receive Queue

InfiniBand provides channel communication semantics (as described in Section 1.2.1) in the form of send and receive operations on a QP. In order to use these operations, it is necessary that the receive work requests are placed before the send operations are issued. This ensures that the CA has enough resources to place the data which it receives. However, this presents a scalability issue when there are multiple QPs communicating. Resources made available to one QP are wasted if there is no more communication with that remote process. To handle such a situation, the IBTA specification version 1.2 introduced a new software service called the *Shared Receive Queue*. This allows the CA to share receive requests for several QPs into one FIFO queue. In addition to providing a scalable mechanism to share receive requests for multiple connections, the SRQ also provides a "Low-watermark" asynchronous service. If the shared receive requests drop below a preset threshold, then the

application (in our case MPI library) may be notified of this event. This event may allow applications to perform flow-control or other operations based on their requirement.

## 1.2.4 Memory Registration

InfiniBand requires that all memory that is used for communication be "registered" before any data is sent or received into it. Registration is a two phase operation in which the pages are marked unswappable (ie. these will no longer be paged out to disk) and the virtual addresses of the pages in concern will be sent to the CA. The reason for this requirement is that when the CA actually performs the communication operation, the data should be present in the RAM and the CA should know its address.

Registration is usually a high-latency blocking operation. In addition, since the memory pages registered cannot be swapped out, the application (running on top of MPI) has lesser physical memory available.

## 1.2.5 Completion and Event Handling Mechanisms

In InfiniBand, the Completion Queue (CQ) provides an efficient and scalable mechanism to report completion events to the application. The CQ can provide completion notifications for both send and receive events as well as many asynchronous events. It supports two modes of usage: i) Polling ii) Asynchronous. In the Polling mode, the application uses an InfiniBand verb to poll the memory locations associated with the completion queue. One or many completion entries may be returned at one go. In the Asynchronous mode, the application need to continuously poll the CQ to look for completions. The CQ will generate an interrupt when a completion event is generated. Further, IBA provides a mechanism by which only "solicited events" may cause interrupts. In this mode, the application can poll the CQ, however on selected types of completions, an interrupt is generated. This mechanism allows

interrupt suppression and thus avoid unnecessary costs (like context-switch) associated with interrupts.

## 1.3 Problem Statement

Cluster computing has become mainstream HPC (High-Performance Computing) now, with 75% of the most powerful parallel computers being clusters. These modern clusters are equipped with powerful interconnects, such as InfiniBand [17]. Scientific applications executing on these clusters use primarily MPI as their programming model. As the size of these clusters continues to increase, it is crucial to design MPI libraries in the most efficient and scalable manner.

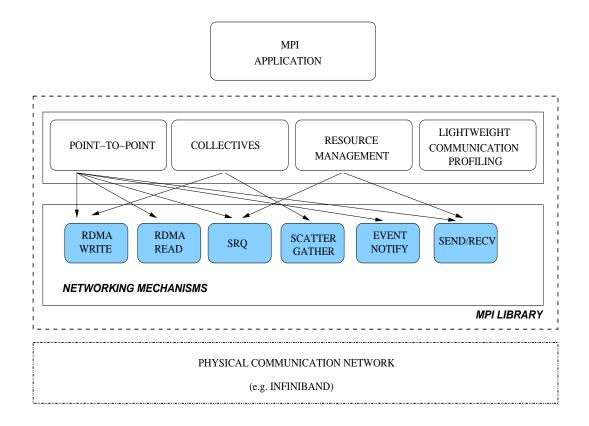

Figure 1.3: Problem Space for this Dissertation

Figure 1.3 shows the scope of this dissertation. In short, we aim to design the point-to-point and collective components of the MPI libraries to make use of novel network primitives in order to make better utilization of resources and be most efficient. We intend to understand the resource usage characteristics and communication patterns of MPI applications not only for optimizing MPI libraries, but also to optimize the end applications/benchmarks themselves. We present the problem statement in details as follows:

- Can we design point-to-point operations in a manner such as to improve computation and communication overlap ratio? The computation and communication overlap ratio is an indication of the amount of computation an MPI application can perform while communication operations are pending. Current generation MPI libraries depend upon the MPI application to invoke communication progress by using MPI routines. This means that computation and communication cannot proceed in parallel. However, independent progress of communication operations is critical to achieving good overall application performance. As far as possible, the performance of the MPI library should not depend on the application calling MPI routines to make progress. With system sizes scaling to the tens-of-thousands of processors, application developers are forced to tackle many complex optimizations. The MPI library should take charge of making sure communication operations can proceed without direct application involvement. Enabling independent communication is a tough challenge, as it involves asynchronous actions to take place while the CPU is busy in computation routines.

- Can the collective operations be designed to leverage modern networking mechanisms and achieve improved latency and scalability? MPI applications often utilize collective communication routines in order to enable the MPI library to optimize performance based on the system architecture/topology. However, MPI libraries often implement

collective operations on top of the point-to-point operations (e.g. MPI\_Send, MPI\_Recv, etc.), adding software overhead and losing the collective operation semantics which leads to lack of optimization opportunities. Designing collective operations directly over raw network primitives is a promising approach to removing software overheads. However, it is a challenge to identify and design the right algorithms and design them in a scalable and high-performance manner.

- Can we leverage newer features of InfiniBand and design newer communication buffer organization techniques which have scalable resource usage? MPI specifies a fully connected model. Under such a model any process can send or receive from any other process. The MPI library needs to reserve some memory to handle the exchange of messages. The amount of communication buffers the MPI library needs should not rapidly increase with the number of processes in the application. Current generation MPI implementations often allocate communication buffer resources on a per remote process basis in order to optimize point-to-point communication performance. Although these approaches provide good performance for small scale clusters, they are simply not viable for larger scale clusters as they require several GigaBytes of memory per process. The challenge is to devise a mechanism which not only allows high-performance for small scale clusters, but scales well for very large clusters with tens-of-thousands of nodes.

- Can the new scalable communication buffer organization achieve similar or better performance than previous designs for a wide variety of MPI applications? MPI applications exhibit a wide variety of communication patterns. For every different communication, buffers may be consumed in different ways. The communication buffer

mechanism must be able to achieve high-performance under most of the highly likely communication patterns, while providing scalable buffer usage. A very detailed study of a variety of MPI applications is required in order to understand the performance characteristics of the buffer management mechanisms. There are no existing profiling tools that offer such detailed information, and in order to study these parameters, a light-weight profiling layer is required inside the MPI library.

• Can we achieve a significantly better understanding of application/benchmark characteristics and requirements, and redesign them according to the strengths of modern interconnects? – As the system sizes increase to tens-of-thousands of nodes, the scope to perform optimization is greatest in the MPI application. Many of the existing MPI codes have been written several years back when the networks didn't offer novel features. Thus, the MPI applications/benchmarks may not be best suited for the modern generation of networks. It is therefore crucial to understand the behavior of these applications and benchmarks and provide insights to real application developers about scalable techniques to employ while writing PetaScale applications.

## 1.4 Research Approaches

In this section we present our general approaches to the above mentioned issues.

1. Designing rendezvous protocol leveraging RDMA Read to enhance computation and communication overlap – We have designed a novel rendezvous protocol which achieves nearly complete computation and communication overlap. We make use the RDMA Read feature offered by InfiniBand and couple it with selective interrupts for enabling the MPI library to make progress even when the application cannot call the MPI library.

- 2. Designing scalable collective operations leveraging lower level RDMA and non-contiguous operations We have designed RDMA based collective operations for two of the commonly used MPI collectives: MPI\_Alltoall and MPI\_Allgather. Our approach cuts down on software overheads bypassing several layers directly to the InfiniBand communication layer and leveraging RDMA and native support for non-contiguous communication.

- 3. Designing scalable communication buffer management techniques We have designed a scalable technique to manage communication buffers utilizing Shared Receive Queues. Using our method, communication buffers need not be dedicated per process, rather, they are used in a FIFO order from a shared pool. We have also designed an associated flow control method with this management scheme.

- 4. In-Depth performance analysis of MPI library with reduced memory usage utilizing internal profiling layers We have analyzed in detail the performance characteristics of our overall designs for a wide variety of end MPI applications. We developed an internal profiling layer to collect information on lower layer events, memory usage to validate design decisions.

- 5. Redesigning application level benchmarks to leverage modern networking capabilities We have redesigned two widely used HPCC [18] benchmarks, High-Performance Linpack and RandomAccess, to better utilize modern network and benefit from advances in MPI design as per the above mentioned work.

#### 1.5 Dissertation Overview

We have presented our research over the next several chapters.

In Chapter 2 we take on the challenge of redesigning the Rendezvous Protocol in order to improve the computation and communication overlap. We leverage the RDMA Read semantics to reduce the number of intermediate messages required to transmit an MPI level message. In addition, we utilize the *selective interrupt* mechanism to insert progress calls inside the MPI library even though the MPI application may be busy in computation. Using our design, the MPI library is able to offer almost complete computation and communication overlap.

In Chapters 3 and 4, we present new designs to take advantage of the advanced features offered by InfiniBand in order to achieve scalable and efficient implementation of the MPI\_Alltoall and MPI\_Allgather collectives. We proposed that the implementation of collectives be done directly on the InfiniBand Verbs Interface rather than using MPI level point-to-point functions. We evaluate our proposed designs in detail Our experimental results and analytical models enable us to conclude that our new designs can be more scalable and efficient than current approaches.

In Chapter 5, we propose a novel Shared Receive Queue based Scalable MPI design. Our design uses low-watermark interrupts to achieve efficient flow control and utilizes the memory available to the fullest extent, thus dramatically improving the system scalability. In addition, we also proposed an analytical model to predict the memory requirement by the MPI library on very large clusters (to the tune of tens-of-thousands of nodes).

As InfiniBand gains popularity and is included in increasingly larger clusters, having a scalable MPI library is imperative. Through our evaluation of the NAS Parallel Benchmarks, SuperLU, NAMD, and HPL in Chapter 6, we explore the impact of reduction of communication memory on the performance. Our evaluation shows that the latest SRQ design

of MVAPICH is able to use a constant amount of internal memory per process with optimal performance, regardless of the number of processes, an order of magnitude lesser than other Eager protocol designs of MVAPICH. In our experiments, only 5-10MB of communication memory was required by the SRQ design to attain the best recorded performance level achievable with MVAPICH.

In Chapter 7, we demonstrate that by revisiting the design of end MPI applications, we can gain significant performance improvement. The communication patterns of these applications and benchmarks need to be studied and modified to take the most advantage out of modern networks and their capabilities. The MPI design parameters can have a significant impact on the performance characteristics of end applications. With the coupling of the application modifications with optimized MPI library design, we can improve overall performance significantly.

#### CHAPTER 2

# IMPROVING COMPUTATION AND COMMUNICATION OVERLAP

MPI provides both blocking and non-blocking semantics of point-to-point communication. Of these, it is widely accepted that non-blocking semantics offer better performance to end-applications by allowing overlap of computation and communication. Applications can use MPI\_Isend, MPI\_Irecv to initiate the communication operations and return to computing. When the application needs the messages, they can call MPI\_Wait. Most high-performance MPI implementations are based on polling progress engines, i.e. the sender and receiver processes must periodically call MPI functions to ensure communication progress. However, due to certain MPI internal protocols (such as Rendezvous protocol), overlap of computation and communication may be hampered. If progress calls are not triggered for a long time, messages may be severely delayed.

In this Chapter, we take on the challenge of redesigning the Rendezvous Protocol in order to improve the computation and communication overlap. We leverage the RDMA Read semantics to reduce the number of intermediate messages required to transmit an MPI level message. In addition, we utilize the *selective interrupt* mechanism to insert progress calls inside the MPI library even though the MPI application may be busy in computation. Using

our design, the MPI library is able to offer almost complete computation and communication overlap. Application wait times can be reduced by 30%.

The rest of the chapter is organized as follows. In Section 2.1 we provide necessary background information for this work. In Section 2.2 we describe current approaches and their limitations. In Section 2.3, we discuss the design alternatives and the final design approach. In Section 2.4, we evaluate our design and provide experimental results. Finally, in Section 2.5 we summarize the results and impact of this work.

## 2.1 Background

In this section, we provide the necessary background details for this work. First, we describe the Rendezvous Protocol, then we describe the RDMA Write and RDMA Read mechanisms of InfiniBand.

#### 2.1.1 Overview of Rendezvous Protocol

The Rendezvous Protocol negotiates the buffer availability at the receiver side before the message is actually transferred. This protocol is used for transferring large messages when the sender is not sure whether the receiver actually has the buffer space to hold the entire message. MVAPICH [34], along with MPICH-GM [33], MPICH-Quadrics [38], utilize RDMA Write to totally eliminate intermediate message copies and efficiently transfer large messages.

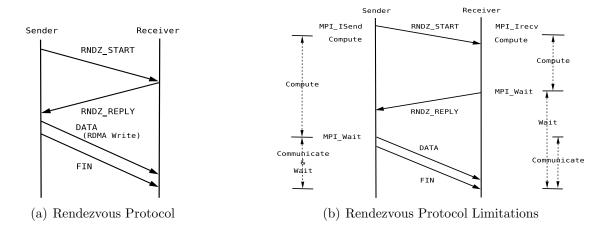

In this protocol, the sending process sends a START message to the receiver along with the message envelope (usually, MPI message matching tags). Upon receipt of this message, the the envelope is buffered. When the matching receive is posted by the receiving MPI application, the receiver side sends a REPLY message with the location of the receiver user buffer. Upon discovery of the REPLY message, the sender sends the actual data DATA message to the receiver. This is followed by a FIN message from the sender indicating end of all data. Thus, the message can be transferred to the receiver. As the data transfer doesn't start until matching receives are posted, only buffering of message envelopes are required.

#### 2.1.2 Overview of InfiniBand RDMA-Write and RDMA-Read

InfiniBand offers two types of memory access semantics, RDMA-Write and RDMA-Read. RDMA stands for *Remote Direct Memory Access*. Using RDMA, a network-interface can access the memory of a remote node transparent to the CPU at the remote node. The CPU is involved only in granting access privileges to the network-interface. Once the access control is set up, the DMA engines at the network-interface directly access memory without any further intervention. This enables the CPU to perform more useful computation work, while leaving networking responsibilities to the NIC. This also aids in reducing the amount of cache pollution. Since memory need no longer be touched by the CPU, it need not be brought back into the various levels of caching hierarchy.

In the RDMA-Write mechanism, the sending process is aware of the remote memory location and has a message to send which fits in the amount of memory available in the remote memory window. The network-interface takes the message contents from memory and places them directly in the memory of the remote process. In RDMA-Read, the originating process can read the remote memory contents with aid from the network-interface at the remote side.

## 2.2 Current Approaches and their Limitations

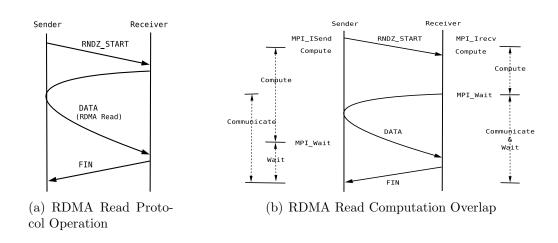

The RDMA Write based protocol is illustrated in Figure 2.1(a). The sending process first sends a control message to the receiver (RNDZ\_START). The receiver replies to the sender

using another control message (RNDZ\_REPLY). This reply message contains the receiving application's buffer information along with the remote key to access that memory region. The sending process then sends the large message directly to the receiver's application buffer by using RDMA Write (DATA). Finally, the sending process issues another control message (FIN) which indicates to the receiver that the message has been placed in the application buffer.

MVAPICH uses a progress engine to discover incoming messages and to make progress on outstanding sends. To achieve low latency, the progress engine senses incoming messages by polling various memory locations. As can be seen in Figure 2.1(a), the RDMA Write based Rendezvous Protocol generates multiple control messages which have to be discovered by the progress engine. Since the progress engine is polling based, it requires the application to call into the MVAPICH library.

However, the MPI applications might be busy doing some computational work or I/O. In this case the applications cannot make any call into the MPI library. As a result, the message transfer has to simply wait until the control messages are discovered. This scenario is illustrated in Figure 2.1(b). The delayed discovery of important control messages leads to serialization of the computation and communication operations. As a result, the overlap potential of computation and communication is severely hampered as shown.

## 2.3 Design Alternatives and Challenges

In this section, we compare RDMA Read and Write as design alternatives and pick the best one of them. We will compare the two based on parameters like: communication progress, computation/communication overlap, number of I/O bus transactions, etc.

Typically, small messages are sent over Eager Protocol (which is copy-based) and larger messages are set over Rendezvous Protocol. According to the MPI specification, only the

Figure 2.1: MVAPICH Rendezvous Protocol and its Limitations

sender can choose the actual protocol efficiently. Particularly, the MPI Specification [30] states that: "The length of the received message must be less than or equal to the length of the receive buffer. An overflow error occurs if all incoming data does not fit, without truncation, into the receive buffer. If a message that is shorter than the receive buffer arrives, then only those locations corresponding to the (shorter) message are modified." According to the requirements imposed by MPI semantics, the receiver may post a much larger buffer than what the sender chooses to send. Since, the choice of size of the message actually sent (not posted size), lies with the sender, the sender can efficiently make a choice of which protocol to use (Eager or Rendezvous).

Now, we consider the case in which the sender decides to use the Rendezvous Protocol for the message transfer. The operation of a RDMA Write based protocol is shown in Figure 2.1(a) and that based on a RDMA Read protocol is shown in Figure 2.2(a). Based on program execution and timing, there can be three cases.

- Sender arrives first: If the sender arrives first at the send call, it can send the RNDZ\_START message immediately. Inside the RNDZ\_START message, it can also embed the virtual address and memory handle information about the buffer to be sent. It is to be noted that upon the receipt of this RNDZ\_START message, all the information about the application buffer is available to the receiving process. Clearly, the receiving process does not need to send a RNDZ\_REPLY message any more. It can simply perform a RDMA Read from the application buffer location of the sending process.

- Receiver arrives first: Even if the receiver arrives first at the receive call, it cannot choose which protocol the message will be actually sent over. So, it must wait for the sender's choice of protocol. The receiver waits for the RNDZ\_START message from the sender. However, once the receiver gets the RNDZ\_START message, it can perform the RDMA Read directly from the sender buffer, without sending any more RNDZ\_REPLY message.

- Sender and receiver arrive at the same time: In this case, the sender and the receiver arrive concurrently. However, neither the sender or the receiver knows whether the other process has arrived. Hence, in this case, the receiver must wait for the protocol choice from sender (as stated before), and the sender must assume that it has arrived first. Hence, again in this case, the optimal choice would be to have the sender send a RNDZ\_START message to the receiver. As stated above, the receiving process can simply perform a RDMA Read from the sender buffer directly.

As per the above three cases, RDMA Read is chosen to reduce the number of control messages. Since the number of control messages is reduced, the total number of I/O bus transactions are reduced too. In addition, since the receiver can progress independently of the

sender (once the RNDZ\_START message is sent), we can enhance the communication progress. Further, even if the sender does not call any MPI progress, the data transfer can proceed over RDMA Read. This leads to much better overlap of computation with communication, if RDMA Read is used.

Thus, we conclude from the above that: the optimal choice of data transfer semantics is RDMA Read in all possible combinations of sender or receiver arriving at the communication point.

Figure 2.2: RDMA Read Based Rendezvous Protocol

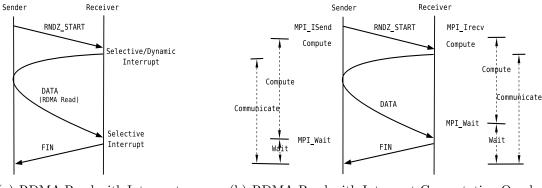

## 2.3.1 RDMA Read with Interrupt Based Rendezvous Protocol

In this section we describe the design of Rendezvous Protocol using RDMA Read with interrupt. As we described earlier in this section, RDMA Read is the best data transfer mechanism when the sender arrives first. However, if the receiver arrives first, it still needs to wait for the RNDZ\_START message from the sender. In the meantime, the receiver might be busy computing. The discovery of this RNDZ\_START message is critical to achieving good

overlap between computation and communication. Since this control message is critical, we can generate an interrupt on its arrival. This message should be handled by an *asynchronous* completion handler. The basic protocol is illustrated in Figure 2.3(a).

Selective Interrupt: Interrupts are usually associated with various overheads. Causing too many interrupts can harm the overall application performance. We devise a method by which we can cause a selective interrupt only on the arrival of RNDZ\_START message and completion of RDMA Read DATA message. In order to have selective interrupts, two things must be done. First, the sender has to set a solicit bit in the descriptor (solicit\_event) of the message which is intended to cause the interrupt. Secondly, the receiver must request for interrupts from the completion queue by setting VAPI\_SOLIC\_COMP prior to the arrival of the message.

Interrupt Suppression: Even though we have a selective interrupt scheme, back-to-back RNDZ\_START messages should not generate multiple interrupts. This will harm the overall application performance. For designing this scheme, we disable any interrupts on the completion queue automatically after the asynchronous event handler is invoked. The event handler then keeps on polling the completion queue until there are no more completion descriptors. Thus, in this design even though back-to-back RNDZ\_START messages might arrive, only one interrupt is generated. Finally, when there are no more completion descriptors left, the asynchronous event handler resets the request for interrupts before exiting.

Dynamic Interrupt Requests: The approximate cost of an interrupt is 18  $\mu$ s on our experimental platform. However, the cost of the receiver requesting an interrupt and clearing it is only 7  $\mu$ s. Our design of RDMA Read with Interrupt, has such a *dynamic* scheme, in which the receiving process requests for interrupts only when pending receives are posted. If no receives are pending, then the request for interrupts is turned off, and the MPI goes

into polling based progress. Whenever the interrupt is set, an internal flag indicates this status. On posting of subsequent receives, this interrupt does not need to be re-requested. Similarly, when the interrupt is cleared, an internal flag indicates that status too. This dynamic scheme can reduce the number of interrupts in the case where the sender arrives first, but the receive application hasn't posted the receive as yet.

Hybrid Communication Progress: In this new design, our asynchronous event handler is invoked by an interrupt. It executes as a separate thread to the MPI program. Many MPI implementations are based on a polling progress engine, including MVAPICH. This means that whenever a MPI call is issued by the application, the MPI implementation checks all communication channels for incoming messages and makes progress on pending sends. Hence, we can potentially have two threads of the progress engine (one polling and the other handling the event) active at the same time. Thus, we need to provide a thread safe mechanism to implement this hybrid progress engine. At the same time as providing thread safety, it should also provide high performance. If there are no interrupts caused, the overhead imposed by this thread safety mechanism should be minimal. Figure 2.3(b) shows the computation/communication at both the sender and receiver side. In this figure, the RNDZ\_START message causes an interrupt at the receiver. The RDMA Read DATA message is issued immediately. Hence, the computation and communication can be overlapped at both sender and receiver.

#### 2.4 Performance Evaluation

In this section we will present the results we obtained with our proposed RDMA Read based Rendezvous protocol. We compare three schemes, the first one being the RDMA Write (MVAPICH version 0.9.5) [34], the second one being the RDMA Read and the third one

(a) RDMA Read with Interrupt Protocol Operation

(b) RDMA Read with Interrupt Computation Overlap

Figure 2.3: RDMA Read with Interrupt based Rendezvous Protocol

being RDMA Read with Interrupt based Rendezvous Protocol. Our evaluation platforms used were of two types:

- Cluster A: 8 SuperMicro SUPER X5DL8-GG nodes with dual Intel Xeon 3.0 GHz processors. Each node has 512KB L2 cache and 2GB of main memory. The nodes are connected to the InfiniBand fabric with 64-bit, 133 MHz PCI-X interface.

- Cluster B: 32 nodes, dual Intel Xeon 2.66 GHz processors. Each node has 512KB L2 cache and 2GB of main memory. The nodes are connected to InfiniBand fabric with 64-bit, 133 MHz PCI-X interface.

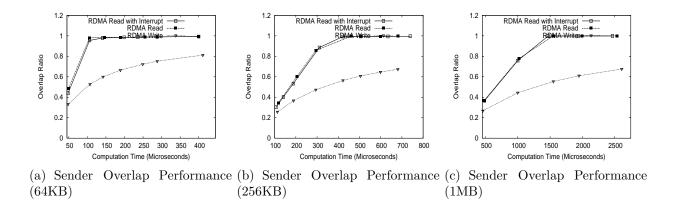

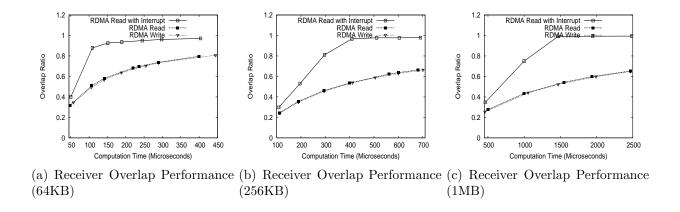

# 2.4.1 Computation and Communication Overlap Performance

In this section we evaluate the ability of our designed schemes to effectively overlap computation and communication. We designed two micro-benchmarks and carried out the evaluation on Cluster A.

Sender Overlap: In this experiment, we evaluate how well the sending process is able to overlap computation with communication. The sender initiates communication using MPI\_Isend, then computes for W  $\mu$ s. At the same time, the receiver is just blocking on a MPI\_Recv. After the sender has finished computing, it checks for completion of the pending sends. The entire operation is timed at the sender. If the entire operation lasted for T  $\mu$ s, then the computation to communication overlap ratio is W/T.

Figure 2.4 shows this ratio versus the computation time. We can see that for the RDMA Write scheme, the overlap ratio is quite low. This is because the sender process is unable to receive the RNDZ\_REPLY message due to the computation. On the other hand, the RDMA Read and RDMA Read with Interrupt schemes show nearly complete overlap. It is to be noted that for low values of computation time (W), the value of the ratio is low, since in this case, the time for communication is dominant.

Receiver Overlap: In this experiment, we evaluate how well the receiving process is able to overlap computation with communication. This experiment is similar in nature with the sender overlap experiment. In this experiment, the receiver posts a receive using MPI\_Irecv and computes for W  $\mu$ s, while the sender blocks on a MPI\_Send. After the computation, the receiver waits for the communication to complete. The entire time is marked as T. The computation to communication ratio is W/T.

Figure 2.5 shows this ratio versus the computation time. We can see that for the RDMA Write and the RDMA Read schemes, the overlap ratio is quite poor. This is because the receiving process is unable to issue the RNDZ\_REPLY or DATA message due to the computation. On the other hand, the RDMA Read with Interrupt scheme show nearly complete overlap, since the arrival of the RNDZ\_START message generates an interrupt and the receiving process

Figure 2.4: Sender Communication and Computation Overlap Performance

Figure 2.5: Receiver Communication and Computation Overlap Performance

Figure 2.6: Computation and Communication Overlap (Sender) with Time Stamps

Figure 2.7: Computation and Communication Overlap (Receiver) with Time Stamps

immediately issues the DATA message. As noted before, for low values of computation time (W), the communication time is dominant, resulting in a low overlap ratio.

The experimental platform is dual SMPs. In the case of RDMA Read with Interrupt scheme, it may happen that the interrupt handler thread is scheduled on the "idle" processor, thus inflating the benefits of RDMA Read with Interrupt. In order to eliminate such an effect, we perform this experiment on a uni-processor kernel on the same machines. Our experiments reveal that with RDMA Read with Interrupt, we get 99.5% overlap, whereas with RDMA Read and RDMA Write we observe only 62.2% and 59% overlap, respectively, for a 1MB message size with 1800  $\mu$ s computation time. These results are almost identical with the dual SMP results. This is because the interrupt handler thread consumes very little CPU time and is very short lived. It needs to be "awake" only for a few micro seconds to perform tag matching and post necessary network transactions only if it is required.

Communication Progress: In this execution, we take consecutive time stamps from the micro-benchmark execution. These time stamps are recorded just before the application enters the computation phase, in the MPI\_Wait and from inside the MPI library when the actual communication takes place.

Figure 2.6 shows the progress snapshot during the sender overlap test. We observe from this figure, that in the RDMA Write based Rendezvous Protocol, the computation and communication are completely serialized. It offers no overlap at all. Whereas, in the RDMA Read based schemes, the communication happens during the application is computing. The RDMA Read based schemes can progress 50% faster when transferring messages of 1MB and computing for 1500  $\mu$ s.

Similarly, Figure 2.7 shows the progress during the receiver overlap test. We observe from this figure, that in the RDMA Write and the RDMA Read based protocol, the computation

and communication are completely serialized. They hardly offer any overlap. Whereas, in the RDMA Read with Interrupt scheme, the communication happens during the application is computing. The RDMA Read with Interrupt schemes can progress around 50% faster when transferring messages of 1MB and computing for 1500  $\mu$ s.

## 2.4.2 Application level Evaluation

In this section, we evaluate the impact of our RDMA Read and RDMA Read with Interrupt schemes on application wait times. For our evaluation, we choose two well known applications - HPL and NAS-SP (Scalar Pentadiagonal Benchmark). High Performance Linpack (HPL) is a well known benchmark for distributed memory computers [2]. It is used to rank the top 500 computers [45] twice every year. NAS-SP [6] is a CFD simulation which solves linear equations for the Navier-Stokes equation. We used the Class C benchmark for our evaluation.

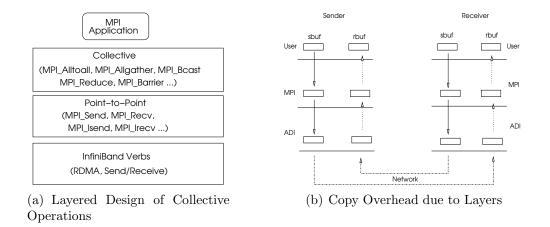

To find out the communication time for these applications, we use a light-weight MPI profiling library [20], mpiP. This profiling tool reports the top aggregate MPI calls and the time spent in each one of them. We collect the aggregate time spent in the MPI\_Wait() function call. This time is spent by the application just busy waiting for the pending sends and receives to be completed. Since this time is just wasted by the application waiting for the network to complete the operations, this represents time which can possibly be overlapped with computation. Figure 2.8(a) and 2.8(b) show the MPI\_Wait times for HPL and NAS-SP (Class C) with increasing number of processes, respectively.

We observe that the wait time of HPL is reduced by around 30% for 32 processes by the RDMA Read and RDMA Read with Interrupt designs. Similarly, for the NAS-SP, we can see around 28% improvement for 36 processes. This is mainly because the RDMA Write

based Rendezvous implementation waits till the MPI\_Wait() to issue the DATA message, and hence cannot achieve good overlap. In addition, we observe from the figure that the benefits provided by the new design are scaling with the number of processes. Hence, our new design is capable of taking better advantage of network when there is possibility of overlap. In these results we see that the RDMA Read and RDMA Read with Interrupt perform equally well. This might be due to the fact that these applications do not require computation/communication overlap on the receiver side.

Figure 2.8: Application Level Evaluation for Rendezvous Protocol Designs

## 2.5 Summary

In this chapter, we have presented new designs which exploit the RDMA Read and the capability of generating selective interrupts to implement a high-performance Rendezvous Protocol. We have evaluated in detail the performance improvement offered by the new design in several different areas of high performance computing. We have observed that the